# SJCET M.Tech (VLSI & ES) Curriculum 2024

# (M.Tech in VLSI and Embedded Systems)

#### **SEMESTER I**

| SLOT | COURSE      | COURSE NAME                            | MA  | RKS | L-T-P | HOURS | CREDIT |

|------|-------------|----------------------------------------|-----|-----|-------|-------|--------|

| 5201 | CODE        |                                        | CIA | ESE | 211   | noons |        |

| А    | 24SJ1TEC100 | ADVANCED<br>ENGINEERING<br>MATHEMATICS | 40  | 60  | 3-0-0 | 3     | 3      |

| В    | 24SJ1TEC006 | CMOS VLSI DESIGN                       | 40  | 60  | 3-0-0 | 3     | 3      |

| С    | 24SJ1TEC007 | FPGA BASED SYSTEM<br>DESIGN            | 40  | 60  | 3-0-0 | 3     | 3      |

| D    | 24SJ1EECXXX | PROGRAM ELECTIVE 1                     | 40  | 60  | 3-0-0 | 3     | 3      |

| E    | 24SJ1EECXXX | PROGRAM ELECTIVE 2                     | 40  | 60  | 3-0-0 | 3     | 3      |

| S    | 24SJ1RGE100 | RESEARCH<br>METHODOLOGY AND<br>IPR     | 40  | 60  | 2-0-0 | 2     | 2      |

| Т    | 24SJ1LEC003 | DESIGN LAB I                           | 100 | P.  | 0-0-2 | 2     | 1      |

|      | C           | Fotal                                  | 340 | 360 | 15-   | 19    | 18     |

Teaching Assistance: 6 hours

#### **PROGRAM ELECTIVE 1**

|      | PROGRAM ELECTIVE 1 |                |                                         |       |       |        |  |  |  |  |

|------|--------------------|----------------|-----------------------------------------|-------|-------|--------|--|--|--|--|

| SLOT | SL<br>NO           | COURSE<br>CODE | COURSE NAME                             | L-T-P | HOURS | CREDIT |  |  |  |  |

|      | 1                  | 24SJ1EEC034    | PHYSICAL DESIGN<br>AUTOMATION           | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 2                  | 24SJ1EEC035    | DESIGN WITH ADVANCED<br>MICROCONTROLLER | 3-0-0 | 3     | 3      |  |  |  |  |

| D    | 3                  | 24SJ1EEC036    | EDA TOOLS                               | 3-0-0 | 3     | 3      |  |  |  |  |

| D    | 4                  | 24SJ1EEC037    | DSP ALGORITHMS AND<br>ARCHITECTURE      | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 5                  | 24SJ1EEC038    | ADVANCED DIGITAL SIGNAL<br>PROCESSING   | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 6                  | 24SJ1EEC007    | ELECTRONIC PACKAGING                    | 3-0-0 | 3     | 3      |  |  |  |  |

### **PROGRAM ELECTIVE 2**

|      | PROGRAM ELECTIVE 2 |                |                                                |       |       |        |  |  |  |

|------|--------------------|----------------|------------------------------------------------|-------|-------|--------|--|--|--|

| SLOT | SL<br>NO           | COURSE<br>CODE | COURSE NAME                                    | L-T-P | HOURS | CREDIT |  |  |  |

|      | 1                  | 24SJ1EEC039    | VLSI SIGNAL PROCESSING                         | 3-0-0 | 3     | 3      |  |  |  |

|      | 2                  | 24SJ1EEC101    | ADVANCED DIGITAL<br>SYSTEM DESIGN              | 3-0-0 | 3     | 3      |  |  |  |

| E    | 3                  | 24SJ1EEC040    | DIGITAL DESIGN PRINCIPLES<br>AND APPLICATIONS  | 3-0-0 | 3     | 3      |  |  |  |

|      | 4 <sub>24SJ1</sub> | 24SJ1EEC041    | FUNCTIONAL VERIFICATION<br>WITH SYSTEM VERILOG | 3-0-0 | 3     | 3      |  |  |  |

|      | 5                  | 24SJ1EEC042    | ASIC DESIGN                                    | 3-0-0 | 3     | 3      |  |  |  |

|      | 6                  | 24SJ1EEC043    | EMBEDDED OPERATING SYSTEM                      | 3-0-0 | 3     | 3      |  |  |  |

|      | 7                  | 24SJ1EEC011 F  | EAL TIME OPERATING SYSTEM                      | 3-0-0 | 3     | 3      |  |  |  |

|      |             | SEMEST                                     | ER II |     |       |       |        |

|------|-------------|--------------------------------------------|-------|-----|-------|-------|--------|

| SLOT | COURSE      | COURSE NAME                                | MA    | RKS | L-T-P | HOURS | CREDIT |

|      | CODE        |                                            | CIA   | ESE |       |       |        |

| А    | 24SJ2TEC100 | FOUNDATIONS OF<br>DATA SCIENCE             | 40    | 60  | 3-0-0 | 3     | 3      |

| В    | 24SJ2TEC004 | ANALOG VLSI DESIGN                         | 40    | 60  | 3-0-0 | 3     | 3      |

| С    | 24SJ2EECXXX | PROGRAM ELECTIVE 3                         | 40    | 60  | 3-0-0 | 3     | 3      |

| D    | 24SJ2EECXXX | PROGRAM ELECTIVE 4                         | 40    | 60  | 3-0-0 | 3     | 3      |

| E    | 24SJ2EECXXX | INDUSTRY/<br>INTERDISCIPLINARY<br>ELECTIVE | 40    | 60  | 3-0-0 | 3     | 3      |

| S    | 24SJ2PEC100 | MINI PROJECT                               | 100   |     | 0-0-4 | 4     | 2      |

| Т    | 24SJ2LEC003 | DESIGN LAB II                              | 100   |     | 0-0-2 | 2     | 1      |

|      | 5           | Fotal                                      | 400   | 300 | F     | 21    | 18     |

Teaching Assistance: 6 hours

|      | PROGRAM ELECTIVE 3                        |                |                                             |       |       |        |  |  |  |  |

|------|-------------------------------------------|----------------|---------------------------------------------|-------|-------|--------|--|--|--|--|

| SLOT | SL<br>NO                                  | COURSE<br>CODE | COURSE NAME                                 | L-T-P | HOURS | CREDIT |  |  |  |  |

|      | 1     24SJ2EEC035     EMBEDDED NETWORKING |                | 3-0-0                                       | 3     | 3     |        |  |  |  |  |

|      | 2                                         | 24SJ2EEC043    | SoC DESIGN                                  | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 3                                         | 24SJ2EEC036    | VLSI STRUCTURE FOR DSP                      | 3-0-0 | 3     | 3      |  |  |  |  |

| С    | 4                                         | 24SJ2EEC037    | SEMICONDUCTOR MEMORIES                      | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 5                                         | 24SJ2EEC038    | EMBEDDED SYSTEM DESIGN                      | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 6                                         | 24SJ2EEC039    | MULTIRATE SIGNAL<br>PROCESSING AND WAVELETS | 3-0-0 | 3     | 3      |  |  |  |  |

### **PROGRAM ELECTIVE 4**

|      | PROGRAM ELECTIVE 4 |                |                           |       |       |        |  |  |  |  |

|------|--------------------|----------------|---------------------------|-------|-------|--------|--|--|--|--|

| SLOT | SL<br>NO           | COURSE<br>CODE | COURSE NAME               | L-T-P | HOURS | CREDIT |  |  |  |  |

|      | 1                  | 24SJ2EEC040    | LOW POWER VLSI            | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 2                  | 24SJ2EEC041    | VLSI SYSTEM TESTING       | 3-0-0 | 3     | 3      |  |  |  |  |

| р    | 3                  | 24SJ2EEC042    | HIGH SPEED DIGITAL DESIGN | 3-0-0 | 3     | 3      |  |  |  |  |

| D    | 4                  | 24SJ2EEC021    | DEEP LEARNING             | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 5                  | 24SJ2EEC044    | STATIC TIMING ANALYSIS    | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 6                  | 24SJ2EEC045    | SIGNAL COMPRESSION        | 3-0-0 | 3     | 3      |  |  |  |  |

#### INTERDISCIPLINARY ELECTIVE

|      | INTERDISCIPLINARY ELECTIVE |                |                                     |       |       |        |  |  |  |  |

|------|----------------------------|----------------|-------------------------------------|-------|-------|--------|--|--|--|--|

| SLOT | SL<br>NO                   | COURSE<br>CODE | COURSE NAME                         | L-T-P | HOURS | CREDIT |  |  |  |  |

|      | 1                          | 24SJ2EEC083    | AUTOMOTIVE ELECTRONICS              | 3-0-0 | 3     | 3      |  |  |  |  |

| E    | 2                          | 24SJ2EEC084    | MEMS AND SENSORS                    | 3-0-0 | 3     | 3      |  |  |  |  |

|      | 3                          | 24SJ2EEC085    | NANO MATERIALS FOR DRUG<br>DELIVERY | 3-0-0 | 3     | 3      |  |  |  |  |

#### **INDUSTRY ELECTIVE**

|      |                | SEMESTE                     | R III            |                            |        |       |        |

|------|----------------|-----------------------------|------------------|----------------------------|--------|-------|--------|

| SLOT | COURSE<br>CODE | COURSE NAME                 | MARKS<br>CIA ESE |                            | L-T-P  | HOURS | CREDIT |

|      |                | TRACH                       | K 1              |                            |        | I     |        |

| A*   | 24SJ3MECXXX    | MOOC                        | com              | o be<br>pleted<br>essfully |        |       | 2      |

| В    | 24SJ3AGEXXX    | AUDIT COURSE                | 40               | 60                         | 3-0-0  | 3     | -      |

| С    | 24SJ3IEC100    | INTERNSHIP                  | 50               | 50                         | 7      |       | 3      |

| D    | 24SJ3PEC100    | DISSERTATION PHASE<br>1     | 100              | 13                         | 0-0-17 | 17    | 11     |

|      |                | TRACK                       | K 2              |                            |        | II    |        |

| A*   | 24SJ3MECXXX    | моос                        | com              | o be<br>pleted<br>essfully | H      |       | 2      |

| В    | 24SJ3AGEXXX    | AUDIT COURSE                | 40               | 60                         | 3-0-0  | 3     | -      |

| С    | 24SJ3IEC100    | INTERNSHIP                  | 50               | 50                         | 13-    | )     | 3      |

| D    | 24SJ3PEC001    | RESEARCH PROJECT<br>PHASE 1 | 100              | -/                         | 0-0-17 | 17    | 11     |

|      | Тс             | otal                        | 190              | 110                        | 5      | 20    | 16     |

Teaching Assistance: 6 hours

\*MOOC Course to be successfully completed before the commencement of fourth semester (starting from semester 1).

|      |                                    |                                                    | AUDIT COURSE                      |       |       |        |

|------|------------------------------------|----------------------------------------------------|-----------------------------------|-------|-------|--------|

| SLOT | SL<br>NO                           | COURSE<br>CODE                                     | COURSE NAME                       | L-T-P | HOURS | CREDIT |

|      | 1                                  | 24SJ3AGE100                                        | 3-0-0                             | 3     | -     |        |

|      | 2                                  | 24SJ3AGE001                                        | ADVANCED ENGINEERING<br>MATERIALS | 3-0-0 | 3     | -      |

|      | 3 24SJ3AGE002 FORENSIC ENGINEERING |                                                    | 3-0-0                             | 3     | -     |        |

|      | 4                                  | 4 24SJ3AGE003 DATA SCIENCE FOR<br>ENGINEERS        |                                   | 3-0-0 | 3     | -      |

|      | 5                                  | 5 24SJ3AGE004 DESIGN THINKING                      |                                   | 3-0-0 | 3     | -      |

|      | 6                                  | 5 24SJ3AGE005 FUNCTIONAL PROGRAMMING<br>IN HASKELL |                                   | 3-0-0 | 3     | -      |

| В    | 7                                  | 24SJ3AGE006                                        | FRENCH LANGUAGE (A1<br>LEVEL)     | 3-0-0 | 3     | _      |

|      | 8                                  | 8 24SJ3AGE007 GERMAN LANGUAGE (A1<br>LEVEL)        |                                   | 3-0-0 | 3     | -      |

|      | 9                                  | 24SJ3AGE008                                        | JAPANESE LANGUAGE (N5<br>LEVEL)   | 3-0-0 | 3     | _      |

|      | 10                                 | 24SJ3AGE009                                        | PRINCIPLES OF AUTOMATION          | 3-0-0 | 3     | -      |

|      | 11                                 | 24SJ3AGE010                                        | REUSE AND RECYCLE<br>TECHNOLOGY   | 3-0-0 | 3     | -      |

|      | 12                                 | 24SJ3AGE011                                        | SYSTEM MODELING                   | 3-0-0 | 3     | -      |

|      | 13                                 | 24SJ3AGE012                                        | EXPERT SYSTEMS                    | 3-0-0 | 3     | -      |

7

|         | SEMESTER IV |                              |     |     |        |       |        |  |  |

|---------|-------------|------------------------------|-----|-----|--------|-------|--------|--|--|

| SLOT    | COURSE      | COURSE NAME                  | MA  | RKS | L-T-P  | HOURS | CREDIT |  |  |

|         | CODE        |                              | CIA | ESE |        |       |        |  |  |

| TRACK 1 |             |                              |     |     |        |       |        |  |  |

| А       | 24SJ4PEC100 | DISSERTATION PHASE<br>II     | 100 | 100 | 0-0-24 | 24    | 16     |  |  |

|         |             | TRACH                        | K 2 |     |        |       |        |  |  |

| А       | 24SJ4PEC001 | RESEARCH PROJECT<br>PHASE II | 100 | 100 | 0-0-24 | 24    | 16     |  |  |

|         | Total       |                              |     | 100 | in     | 24    | 16     |  |  |

Teaching Assistance: 5 hours

# **SYLLABUS**

# M. Tech. ELECTRONCS AND COMMUNICATION ENGINEERING (VLSI & EMBEDDED SYSTEMS) 2024 SCHEME

www.sjcetpalai.ac.in

# AUTONOMOUS

Developing into a world class, pace setting institute of Engineering and Technology with distinct identity and character, meeting the goals and aspirations of the society.

# Mission

- To maintain a conducive infrastructure and learning environment for world class education.

- To nurture a team of dedicated, competent and researchoriented faculty.

• To develop students with moral and ethical values, for their successful careers, by offering variety of programs and services.

# Department of Electronics and Communication Engineering

Vision —•

Develop into a center of excellence in Electronics and Communication Engineering contributing to socio-economic progress.

• Mission — •

- To develop and maintain adequate infrastructure for a pacesetting Electronics and Communication engineering.

- To bring up a team of committed, proficient and researchoriented electronics and communication engineering faculty.

- To nurture students into ethical, emotionally strong and technically competent graduates to meet the dynamic challenges of the society.

# Programme Outcomes (POs)

- **PO1:** An ability to independently carry out research/investigation and development work in engineering and allied streams

- **PO2:** An ability to communicate effectively, write and present technical reports on complex engineering activities by interacting with the engineering fraternity and with society at large.

- **PO3:** An ability to demonstrate a degree of mastery over the area as per the specialization of the program. The mastery should be at a level higher than the requirements in the appropriate bachelor's program

- **PO4:** An ability to apply stream knowledge to design or develop solutions for realworld problems by following the standards.

- **PO5:** An ability to identify, select and apply appropriate techniques, resources and state- of-the-art tools to model, analyze and solve practical engineering problems.

- **PO6:** An ability to engage in lifelong learning for the design and development related to the stream-related problems taking into consideration sustainability, societal, ethical and environmental aspects

- **PO7:** An ability to develop cognitive load management skills related to project management and finance which focus on Entrepreneurship and Industry relevance.

# (Programme Specific Outcomes (PSOs)

Post Graduates of the program will be able to:

- Acquire competency in areas of VLSI and Embedded Systems, IC Fabrication, Design, Testing, Verification and prototype development focusing on applications.

- Integrate multiple sub-systems to develop System On Chip, optimize its performance and excel in industry sectors related to VLSI/ Embedded domain.

# SEMESTER I

| SLOT  | COURSE      | COURSE NAME                                | MA  | RKS | L-T-P | HOURS | CREDIT |

|-------|-------------|--------------------------------------------|-----|-----|-------|-------|--------|

| SLUI  | CODE        | COURSE NAME                                | CIA | ESE | L-I-F | nouks | CREDIT |

| А     | 24SJ1TEC100 | ADVANCED<br>ENGINEERING<br>MATHEMATIC<br>S | 40  | 60  | 3-0-0 | 3     | 3      |

| В     | 24SJ1TEC006 | CMOS VLSI DESIGN                           | 40  | 60  | 3-0-0 | 3     | 3      |

| С     | 24SJ1TEC007 | FPGA BASED SYSTEM<br>DESIGN                | 40  | 60  | 3-0-0 | 3     | 3      |

| D     | 24SJ1EECXXX | PROGRAM ELECTIVE 1                         | 40  | 60  | 3-0-0 | 3     | 3      |

| Е     | 24SJ1EECXXX | PROGRAM ELECTIVE 2                         | 40  | 60  | 3-0-0 | 3     | 3      |

| S     | 24SJ1RGE100 | RESEARCH<br>METHODOLOGY<br>AND IPR         | 40  | 60  | 2-0-0 | 2     | 2      |

| Т     | 24SJ1LEC003 | DESIGN LAB I                               | 100 |     | 0-0-2 | 2     | 1      |

| Total | C           |                                            | 340 | 360 | 1     | 19    | 18     |

Teaching Assistance: 6 hours

| CODE            | COURSE NAME                            | CATEGORY           | L | Τ | Р | CREDIT |

|-----------------|----------------------------------------|--------------------|---|---|---|--------|

| 24SJ1TE<br>C100 | ADVANCED<br>ENGINEERING<br>MATHEMATICS | DISCIPLINE<br>CORE | 3 | 0 | 0 | 3      |

**Preamble:** The purpose of this course is to expose students to the basic theory of linear algebra and probability.

**Course Outcomes:** The COs shown are only indicative. For each course, there can be 4 to 6 COs. After the completion of the course the student will be able to

| CO 1 | To analyze distributions of random variables and make computations based on that       |

|------|----------------------------------------------------------------------------------------|

| CO 2 | evaluate average behaviour of random variables, and analyze their converging behviours |

| CO 3 | To analyze behaviour of random processes and explain basis of vector spaces.           |

| CO 4 | To evaluate properties of linear transformations                                       |

| CO 5 | To evaluate if a linear tranformaion is diagonalizable and decompose it using          |

| 000  | spectral decomposition theorem.                                                        |

# Mapping of course outcomes with program outcomes SEPH'S

|      | 2    | O AND       | 199         | COLLEGE OF ENGINEERING |                |         |            |      |      |

|------|------|-------------|-------------|------------------------|----------------|---------|------------|------|------|

|      | PO 1 | <b>PO 2</b> | <b>PO 3</b> | PO4                    | PO5            | PO6     | <b>PO7</b> | PSO1 | PSO2 |

| CO 1 | 3    |             | 3           |                        | - <b>3</b> P A | . A 13- |            |      |      |

| CO 2 | 3    | North Color | 3           | A                      | UTON           | DM3DU   | S          |      |      |

| CO 3 | 3    |             | 3           |                        | 3              | 3       |            |      |      |

| CO 4 | 3    |             | 3           |                        | 3              | 3       |            |      |      |

| CO 5 | 3    |             | 3           |                        | 3              | 3       |            |      |      |

#### **Assessment Pattern**

| <b>Bloom's Category</b> | End Semester Examination |

|-------------------------|--------------------------|

| Apply                   | 20                       |

| Analyse                 | 20                       |

| Evaluate                | 20                       |

| Create                  |                          |

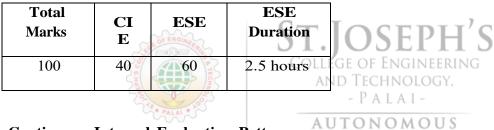

| Total Marks | CIE | ESE | ESE Duration |

|-------------|-----|-----|--------------|

| 100         | 40  | 60  | 2.5 hours    |

#### **Continuous Internal Evaluation Pattern:**

Continuous Internal Evaluation: 40 marks

| Micro project/Course based project | : | 20marks  |

|------------------------------------|---|----------|

| Course based task/Seminar/Quiz     | : | 10marks  |

| Test paper, 1 no.                  | : | 10 marks |

The project shall be done individually. Group projects are not permitted. The project may include the implementation of theoretical computation using software packages. The test papers hall includes a minimum 80% of the syllabus.

### End Semester Examination Pattern:

End Semester Examination: 60 marks

There will be two parts; Part A and Part B ST. JOSEPH'S

- Part A will contain 5 numerical/short answer questions with 1 question from each module, having 5 marks for each question. Students should answer all questions.

- Part B will contain 7 questions with minimum one question from each module of which student should answer any five. Each question can carry 7 marks.

# Syllabus

**Module 1** Axiomatic definition of probability. Independence. Bayes' theorem and applications. Random variables. Cumulative distribution function, Probability Mass Function, Probability Density function, Conditional and Joint Distributions and densities, Independence of random variables. Functions of Random Variables: Two functions of two random variables. Pdf of functions of random variables using Jacobian.

**Module 2** Expectation, Fundamental theorem of expectation, Moment generating functions, Characteristic function. Conditional expectation. Covariance matrix. Uncorrelated random variables. Pdf of Jointly Gaussian random variables, Markov and Chebyshev inequalities, Chernoff bound. Central Limit theorem. Convergence of random variables. Weak law of large numbers, Strong law of large numbers.

**Module 3** Random Processes. Poisson Process, Wiener Process, Markov Process, Birth- Death Markov Chains, Chapman- Kolmogorov Equations,

Groups, Rings, homomorphism of rings. Field. Vector Space. Subspaces. direct sum. Linear independence, span. Basis. Dimension. Finite dimensional vector spaces. Coordinate representation of vectors. Row spaces and column spaces of matrices.

**Module 4** Linear Transformations. Four fundamental subspaces of a linear transformation. Rank and Rank-nullity theorem. Matrix representation of linear transformation. Changeof basis transformation. System of linear equations. Existence and uniqueness of solutions. Linear functionals. Dual, double dual and transpose of a linear transformation.

Module 5 Eigen values, Eigen vectors, Diagonizability.

Inner product. Norm. Projection. Least-squares solution. Cauchy-Schwartz inequality. Orthonormal bases. Orthogonal complement. Spectral decomposition theorem.

# **M.TECH DEGREE EXAMINATION SEMESTER: ADVANCED ENGINEERING MATHEMATICS**

#### **Time: 2.5 Hours**

Marks: 60

#### Part A

#### Answer ALL Questions. Each question carries 5 marks

1. Given that  $ff(x) = \frac{k}{2x}$  is a probability distribution of a random variable that can take

on the values x = 0,1,2,3,A 4. Find k. Find the cumulative distribution function.

- 2. State and prove weak law of large numbers.

- 3. Show that (1,3,2,-2), (4,1,-1,3), (1,1,2,0), (0,0,0,1) is a basis for  $\mathbb{R}^4$ .

- 4. Let  $T: V \to W$  be a linear transformation defined by T(x, y, z) = (x + y, x y, 2x + y, z)z). Find the range, null space, rank and nullity of T.

- 5. Describe an inner product space. If V is an inner product space, then for any vectors  $\alpha, \beta$  in V prove that  $\|\alpha + \beta\| \le \|\alpha\| + \|\beta\|$ .

### Part B Answer ANY FIVE Questions, one from each module $(5 \times 7 \text{ marks} = 35 \text{marks})$

- 6. If the probability mass function of a RV X is given by  $P(X = x) = kx^3$ , x = 1,2,3,4. Find the value of k,  $P \bigoplus_{k=1}^{\infty} < X < \frac{3}{2} \bigvee X > 1 \otimes$  mean and variance of X.

- 7. If the moment generating function of a uniform distribution for a random variable X is  $\frac{1}{2}(e^{5t}-e^{4t})$ . Find E(X).

- 8. Consider the Markov chain with three states,  $s=\{1,2,3\}$  that has the following

transition matrix  $P = \begin{bmatrix} 1 & 1 & 1 \\ 1^2 & 4 & 4 \\ 0 & 2 \end{bmatrix}$  Draw the state diagram for the chain. If  $P(X = \begin{bmatrix} 3 & 1 \\ 1 & 1 \\ -1 & -1 \end{bmatrix}$

1) =

$$P(X_2 = 2) = \frac{1}{4}$$

, find  $P(X_1 = 3, X_2 = 2, X_3 = 1)$ .

9. Find the eigen values and eigen vectors of A = 4 3 1 1 2 2

- 10. Find the least square solution to the equation Ax = b, where  $A = \begin{cases} 1 & 2 \\ 4 & 3 \\ 0 & 0 \end{cases}$

- 4  $\bullet$  Obtain the projection matrix *P* which projects *b* on to the column space of *A*. 6

- Let T be the linear transformation from R<sup>3</sup> to R<sup>2</sup> defined by T(x,y,z) =(x+y, 2z-x). Let B<sub>1</sub>, B<sub>2</sub> be standard ordered bases of R<sup>3</sup> and R<sup>2</sup> respectively. Compute the matrix of T relative to the pair B<sub>1</sub>, B<sub>2</sub>.

- 12. Let V be a finite-dimensional complex inner product space, and let T be any linear operator on V. Show that there is an orthonormal basis for V in which the matrix of T is upper triangular.

\*\*\*\*\*

# Department of ELECTRONICS & COMMUNICATION ENGINEERING

| No  | Торіс                                                                                                                      | No. of<br>Lectures |

|-----|----------------------------------------------------------------------------------------------------------------------------|--------------------|

|     | Module I                                                                                                                   |                    |

| 1.1 | Axiomatic definition of probability. Independence. Bayes' theorem and applications.                                        | 2                  |

| 1.2 | Random variables. Cumulative distribution function, Probability<br>Mass Function,                                          | 1                  |

| 1.3 | Probability Density function, Conditional and Joint Distributions<br>and densities, Independence of random variables.      | 2                  |

| 1.4 | Functions of Random Variables: Two functions of two random variables. Pdf of functions of random variables using jacobian. | 2                  |

|     | Module II                                                                                                                  |                    |

| 2.1 | Expectation, Fundamental theorem of expectation, Conditional expectation.                                                  | 1                  |

| 2.2 | Moment generating functions, Charectristic function.                                                                       | 1                  |

| 2.3 | Covariance matrix. Uncorrelated random variables. Pdf of Jointly Guassian random variables,                                | 2                  |

| 2.4 | Markov and Chebyshev inequalities, Chernoff bound. Central<br>Limit theorem.                                               | 2                  |

| 2.5 | Convergence of random variables. Weak law of large numbers,<br>Strong law of large numbers.                                | 2                  |

| 3   | Module III                                                                                                                 |                    |

| 3.1 | Random Processes. Poisson Process, Wiener Process,                                                                         | 2                  |

| 3.2 | Markov Process, Birth-Death Markov Chains, Chapman-<br>Kolmogorov Equations,                                               | 2                  |

| 3.3 | Groups, Rings, homomorphism of rings. Field. Vector Space.<br>Subspaces. direct sum.                                       | 2                  |

| 3.4 | Linear independence, span. Basis. Dimension. Finite dimensional vector spaces.                                             | 2                  |

| 3.5 | Coordinate representation of vectors. Rowspaces and column spaces of matrices.                                             | 1                  |

| 4   | Module IV                                                                                                                  |                    |

| 4.1 | Linear Transformations. Four fundamental subspaces of a linear transformation. Rank and Rank-nullity theorem.              | 2                  |

| 4.2 | Matrix representation of linear transformation. Change of basis transformation.                                            | 1                  |

| 4.3 | System of linear equations. Existence and uniqueness of solutions.                                                         | 2                  |

| 4.4 | Linear functionals. Dual, double dual and transpose of a linear transformation.                                            | 2                  |

# Department of ELECTRONICS & COMMUNICATION ENGINEERING 5 | Module V

| 5   | Module V                                                         |   |  |  |  |  |  |  |

|-----|------------------------------------------------------------------|---|--|--|--|--|--|--|

| 5.1 | Eigen values, Eigen vectors, Diagonizability.                    | 2 |  |  |  |  |  |  |

| 5.2 | Inner product. Norm. Projection. Least-squares solution. Cauchy- | 2 |  |  |  |  |  |  |

| 5.2 | Schwartz inequality.                                             | 2 |  |  |  |  |  |  |

| 5.3 | Orthonormal bases. Orthogonal complement. Spectral               | r |  |  |  |  |  |  |

| 5.5 | decomposition theorem.                                           |   |  |  |  |  |  |  |

# **Reference Books**

1. Hoffman Kenneth and Kunze Ray, Linear Algebra, Prentice Hall of India.

2. Jimmie Gilbert and Linda Gilbert, Linear Algebra and Matrix Theory, Elsevier

3. Henry Stark and John W. Woods "Probability and Random Processes withApplications to Signal Processing", Pearson Education, Third edition.

4. Athanasios Papoulis and S. Unnikrishna Pillai. Probability, Random Variables and Stochastic Processes, TMH

Department of ELECTRONICS & COMMUNICATION ENGINEERING

| CODE            | COURSE NAME      | CATEGORY          | L | Т | Р | CREDIT |

|-----------------|------------------|-------------------|---|---|---|--------|

| 24SJ1TE<br>C006 | CMOS VLSI DESIGN | PROGRAM<br>CORE 1 | 3 | 0 | 0 | 3      |

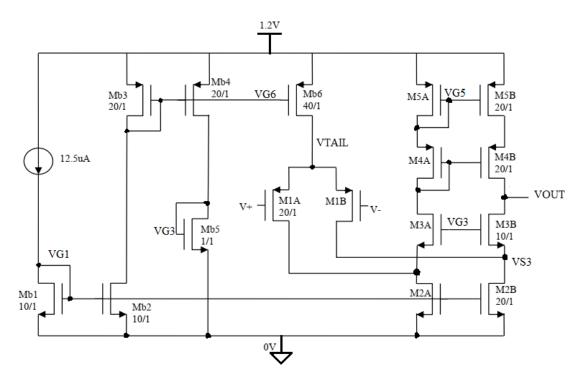

**Preamble:** This course aims to develop students a good knowledge of all aspects of CMOS VLSI Design, its characteristics, designing and model various subsystems using CMOS logic.

**Course Outcomes:** After the completion of the course the student will be able to:

| CO 1                                                                                                             | Design Basic CMOS Digital Circuits.                      |  |  |  |      |                                                                   |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|------|-------------------------------------------------------------------|

| CO 2 Demonstrate Delay Models, Interconnect, Power Analyses, I/O and Clockin<br>Issues of CMOS Digital Circuits. |                                                          |  |  |  |      |                                                                   |

|                                                                                                                  |                                                          |  |  |  | CO 3 | Design Various Types of Static and Dynamic Digital CMOS Circuits. |

| CO 4                                                                                                             | Demonstrate the Timing Concepts in Latch and Flip-Flops. |  |  |  |      |                                                                   |

| CO 5                                                                                                             | Design CMOS Data Path Subsystems and Memory Arrays.      |  |  |  |      |                                                                   |

#### Mapping of Course Outcomes with Program Outcomes

|      | PO 1 | PO 2     | PO 3 | <b>PO 4</b>      | PO 5        | PO 6                              | PO 7 | PSO1 | PSO2 |

|------|------|----------|------|------------------|-------------|-----------------------------------|------|------|------|

| CO 1 | 3    | AF ENGIN | 3    | <b>2</b>         | <b>U</b> SE | $\mathbf{D}\mathbf{Z}\mathbf{I}'$ |      | 1    |      |

| CO 2 |      |          | 2 3  | 2.1              |             | 2                                 | J _  | 2    | 1    |

| CO 3 | 3    |          | 3    | CQLLEG           | E OF3ENG    | INEE2ING                          | 1    | 2    |      |

| CO 4 |      |          | 2 3  | 2 <sup>AND</sup> |             | 2                                 | -    | 2    | 2    |

| CO 5 | 3    | PALAL P  | 3    | 2                | 3           | 2                                 | 1    | 2    | 3    |

AUTONOMOUS

#### **Assessment Pattern**

| <b>Bloom's Category</b> | End Semester Examination |

|-------------------------|--------------------------|

| Apply                   | 30 %                     |

| Analyse                 | 30 %                     |

| Evaluate                | 30 %                     |

| Create                  | 10 %                     |

#### **Mark Distribution**

| Total<br>Marks | CIE | ESE | ESE<br>Duration |  |

|----------------|-----|-----|-----------------|--|

| 100            | 40  | 60  | 2.5 hours       |  |

# Department of **ELECTRONICS** & **COMMUNICATION ENGINEERING Continuous Internal Evaluation Pattern:**

Micro project/Course based project : 20 marks Course based task/Seminar/Quiz : 10 marks Test paper, 1 no. : 10 marks The project shall be done individually. Group projects not permitted. Test paper shall include minimum 80% of the syllabus.

# End Semester Examination Pattern:

The end semester examination will be conducted by the institute. There will be two parts; Part A and Part B. Part A contain 5 numerical questions (such questions shall be useful in the testing of knowledge, skills, comprehension, application, analysis, synthesis, evaluation and understanding of the students), with 1 question from each module, having 5 marks for each question. Students shall answer all questions. Part B contains 7 questions (such questions shall be useful in the testing of overall achievement and maturity of the students in a course, through long answer questions relating to theoretical/practical knowledge, derivations, problem solving and quantitative evaluation), with minimum one question from each module of which student shall answer any five. Each question can carry 7 marks. Total duration of the Examination will be 150 minutes.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 'S COLLEGE OF ENGINEERING<br>OLOGY, PALAI (AUTONOMOU                                      | -                 | Name                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------|-------------------------|

| FIRST SEME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | STER M.TECH DEGREE EXAMI                                                                  | INATION           | Register No:            |

| Course<br>code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24SJ1TEC006                                                                               | Course name       | CMOS VLSI<br>DESIGN     |

| Max. Marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60                                                                                        | Duration          | 2.5 Hours               |

| I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PART A (Answer all questions. Eac                                                         | h question carri  | es 5 marks )            |

| <b>1.</b> Illustra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | te different Types of Power Dissipation                                                   | on in CMOS.       |                         |

| 2. Demon crossta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | strate the crosstalk effects in interco<br>lk.                                            | nnect used in ICs | s. How can we eliminate |

| <b>3.</b> Illustrateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminateliminat | te the problem of monotonicity in a ated.                                                 | dynamic CMOS      | circuits. How it can be |

| 4. Disting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | uish Max-Delay Constraints and Min                                                        | -Delay Constrain  | ts.                     |

| 5. Discuss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | s Embedded DRAM.                                                                          |                   |                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PART B (Answer any 5 questions                                                            | . Each question   | carries 7 marks )       |

| 6. Sketch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | the DC characteristics of CMOS inve                                                       | erter. <b>CFD</b> | ĬŚ                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | a 3 input AND gate with equal rise a twork. Find the worst-case Elmore pa                 |                   |                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | er a 3 <mark>mm-long</mark> , 100nm wide wire. Th<br>tance is 0.2 fF/μm. Construct a π-mo |                   |                         |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | a 3-input BiCMOS NAND gate. L effort.                                                     | abel the transist | or widths. What is the  |

| <b>10.</b> Discus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | s the concept of TSPC based latches.                                                      |                   |                         |

| <b>11.</b> Illustra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ate the booth encoding techniques use                                                     | d in multipliers  |                         |

| 12. Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 6T SRAM cell. How read and write                                                        | operations are pe | rformed.                |

# Department of ELECTRONICS & COMMUNICATION ENGINEERING Syllabus

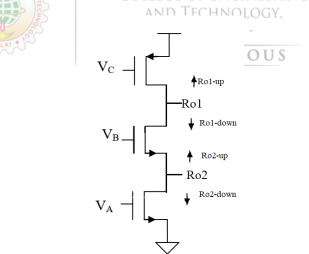

#### Module I (7 Hrs)

**Introduction to CMOS technology**: MOS Transistor operations (Enhancement and depletion type), Structured Design -Y Diagram.

**Static CMOS Inverter**: DC Characteristics, Beta Ratio Effects, Noise Margin- Basics, Pass Transistor DC Characteristics.

**Power analysis**: Types of Power Dissipation, On-Chip Power Distribution Network. On- Chip Bypass Capacitance, Power Network Modelling, Power Supply Filtering, Charge Pumps. Energy Scavenging.

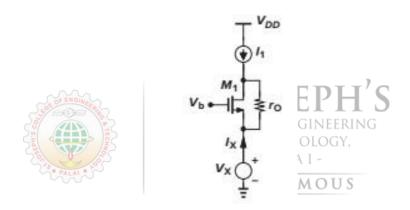

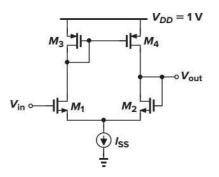

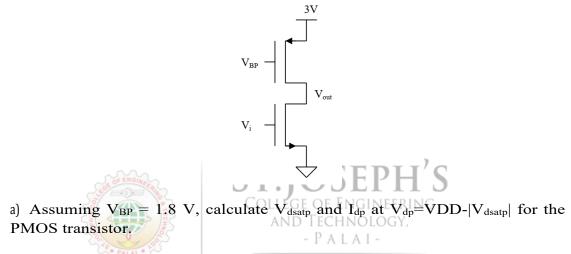

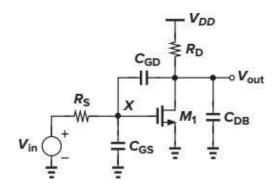

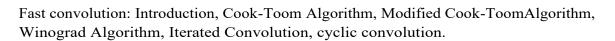

Module II (10 Hrs)